To know about the different IC fabrication techniques, click on the link below.

TAKE A LOOK : IC FABRICATION TECHNIQUES

ION IMPLANTATION

Ion Implantation is an alternative to a deposition diffusion and is used to produce a shallow surface region of dopant atoms deposited into a silicon wafer. This technology has made significant roads into diffusion technology in several areas. In this process a beam of impurity ions is accelerated to kinetic energies in the range of several tens of kV and is directed to the surface of the silicon. As the impurity atoms enter the crystal, they give up their energy to the lattice in collisions and finally come to rest at some average penetration depth, called the projected range expressed in micro meters. Depending on the impurity and its implantation energy, the range in a given semiconductor may vary from a few hundred angstroms to about 1micro meter. Typical distribution of impurity along the projected range is approximately Gaussian. By performing several implantations at different energies, it is possible to synthesize a desired impurity distribution, for example a uniformly doped region.

Ion Implantation System

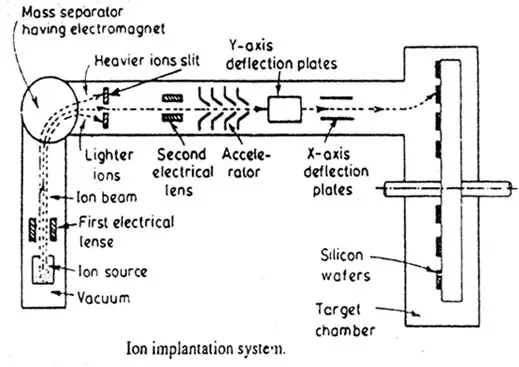

A typical ion-implantation system is shown in the figure below.

A gas containing the desired impurity is ionized within the ion source. The ions are generated and repelled from their source in a diverging beam that is focussed before if passes through a mass separator that directs only the ions of the desired species through a narrow aperture. A second lens focuses this resolved beam which then passes through an accelerator that brings the ions to their required energy before they strike the target and become implanted in the exposed areas of the silicon wafers. The accelerating voltages may be from 20 kV to as much as 250 kV. In some ion implanters, the mass separation occurs after the ions are accelerated to high energy. Because the ion beam is small, means are provided for scanning it uniformly across the wafers. For this purpose the focussed ion beam is scanned electrostatically over the surface of the wafer in the target chamber.

Repetitive scanning in a raster pattern provides exceptionally uniform doping of the wafer surface. The target chamber commonly includes automatic wafer handling facilities to speed up the process of implanting many wafers per hour.

Properties of Ion Implantation

The depth of penetration of any particular type of ion will increase with increasing accelerating voltage. The penetration depth will generally be in the range of 0.1 to 1.0 micro meters.

Annealing after Implantation

After the ions have been implanted they are lodged principally in interstitial positions in the silicon crystal structure, and the surface region into which the implantation has taken place will be heavily damaged by the impact of the high-energy ions. The disarray of silicon atoms in the surface region is often to the extent that this region is no longer crystalline in structure, but rather amorphous. To restore this surface region back to a well-ordered crystalline state and to allow the implanted ions to go into substitutional sites in the crystal structure, the wafer must be subjected to an annealing process. The annealing process usually involves the heating of the wafers to some elevated temperature often in the range of 1000°C for a suitable length of time such as 30 minutes.

Laser beam and electron-beam annealing are also employed. In such annealing techniques only the surface region of the wafer is heated and re-crystallized. An ion implantation process is often followed by a conventional-type drive-in diffusion, in which case the annealing process will occur as part of the drive-in diffusion.

Ion implantation is a substantially more expensive process than conventional deposition diffusion, both in terms of the cost of the equipment and the throughput, it does, however, offer following advantages.

Advantages of Ion Implantation

Ion implantation provides much more precise control over the density of dopants deposited into the wafer, and hence the sheet resistance. This is possible because both the accelerating voltage and the ion beam current are electrically controlled outside of the apparatus in which the implants occur. Also since the beam current can be measured accurately during implantation, a precise quantity of impurity can be introduced. Tins control over doping level, along with the uniformity of the implant over the wafer surface, make ion implantation attractive for the IC fabrication, since this causes significant improvement in the quality of an IC.

Due to precise control over doping concentration, it is possible to have very low values of dosage so that very large values of sheet resistance can be obtained. These high sheet resistance values are useful for obtaining large-value resistors for ICs. Very low-dosage, low-energy implantations are also used for the adjustment of the threshold voltage of MOSFET’s and other applications.

An obvious advantage of implantation is that it can be done at relatively low temperatures, this means that doped layers can be implanted without disturbing previously diffused regions. This means a lesser tendency for lateral spreading.

High-Current High-Energy Implantation Machines

The ion-implantation apparatus, discussed above, has limits to energy range. The minimum implantation energy is usually set by the extraction voltage, that is, the voltage causing the ions to move out of the ion source into the mass separator. This voltage (which is typically 20 KeV) cannot be reduced too far without drastically reducing beam current. The maximum implantation energy is set by the design of the high voltage equipment. The only way to circumvent this is to implant multiply-charged ions.

High beam currents are obtained by using multiple extraction electrodes and higher voltages. To get a final beam of suitable energy a combination of acceleration and deceleration modes of operation is used.

The electrostatic scanning is not suitable for high-beam currents, as it disrupts space charge neutrality and leads to beam “blow-up”. Therefore a mechanical scanning system is usually used. In this case, the wafer is scanned past a stationary beam. This method has the added advantage of keeping the same beam angle across the whole wafer, whereas an electrostatic system can vary by ±2° for 100 mm wafers. However, mechanical scanning puts new requirements on the wafer holder.

High-energy implantation, at MeV energies, makes possible several new processing techniques required for VLSI.

High-energy implantation machines however introduce high-voltage breakdown problem. At about 400 KeV of energy electrical breakdown of the air around the high voltage equipment occurs. Hence, above 400 KeV, conventional equipment is used. Also, high energy implants frequently require water stages heated up to 600 degree Celsius, so that self annealing during implantation minimizes damage in the surface layer. Mechanical scanning is used because of the difficulty of electrostatically scanning a high-energy beam.

Problems in VLSI Processing

Now a day’s large diameter wafers are feasible. Large size wafers are necessary for VLSI. This makes the task of uniformly implanting a wafer increasingly difficult. This in turn has effect on sheet resistance. Ion implantation is basically clean process because contaminant ions are separated from the beam before they hit the target. There are still several sources of contamination possible near the end of the beam line, which can result in contaminant dose up to 10 percent of the intended ion dose, for example, metal atoms knocked from chamber walls, water holder, masking aperature and so on.

Annealing, as discussed earlier, is required to repair lattice damage and put dopant atoms on substitutional site where they will be electrically active. The success of annealing is often measured in terms of the fraction of the dopant that is electrically active, as found experimentally using a Hall Effect technique. For VLSI, the challenge in annealing is not simply to repair damage and activate dopant, but to do so while minimizing diffusion so that shallow implants remain shallow. This has motivated much work in rapid thermal annealing (RTA), where annealing times are on the order of seconds. RTA uses tungsten-halogen lamps or graphite resistive strips to heat the wafer from one or both sides as against conventional furnace annealing where times or on the order of minutes.

Modern device structures, such as the lightly-doped drains (LDD) for MOSFET, require precise control of dopant distribution vertically and lateral on a very fine scale. For VLSI CMOS structure, we need to form shallow n and layers with implantation energies within the reach of standard machines. As stated earlier, the ion velocity, perpendicular to the surface, determines the projected range of an implanted ion distribution. If the water is tilted at a large angle to the ion beam then the effective ion energy is greatly reduced tilted ion beams, thus, make it possible to achieve extremely shallow dopant distributions using comparatively high implantation energies. We can circumvent the problem of implanting a shallow layer in silicon completely if instead we implant entirely into a surface layer and then diffuse the dopant into the substrate. This is most often done when the surface film is to be used as a conductor making contact to the substrate. Diffusion results in steep dopant profiles without damage to the silicon lattice. Dopant diffusion in silicides and polysilicon is generally much faster than in single-crystal silicon, so the implanted atoms soon become uniformly distributed in the film.

Importance of Ion Implantation for VLSI Technology

Ion implantation is a very popular process for VLSI because it provides more precise control of dopants (as compared to diffusion). With the reduction of device sizes to the submicron range, the electrical activation of ion-implanted species relies on a rapid thermal annealing technique, resulting in as little movement of impurity atoms as possible. Thus, diffusion process has become less important than methods for introducing impurity atoms into silicon for forming very shallow junctions, an important feature of VLSI circuits. Ion, implantation permits introduction of the dopant in silicon that is controllable, reproducible and free from undesirable side effects. Over the past few years, ion implantation has been developed into a very powerful tool for IC fabrication. Its attributes of controllability and reproducibility make it a very versatile tool, able to follow the trends to finer-scale devices. Ion implantation continues to find new applications in VLS technologies.

13 Comments

Very useful points. Covered whole parts of matter.

It’s a good site compare to others.

Thank you.

Thanks a ton!! I’m studying VLSI from here only! Very well explained.

Thank you very much.

It is very imformative.

thank u .very important things u have send.thanks most

update infomation on latest news about circuittoday