Take a look at the previous articles.

TAKE A LOOK : INTRODUCTION TO PIC 167F877

TAKE A LOOK : PIC 16F877 – ARCHITECTURE AND MEMORY ORGANIZATION

TAKE A LOOK : REGISTER MEMORY ORGANIZATION IN PIC 16F877

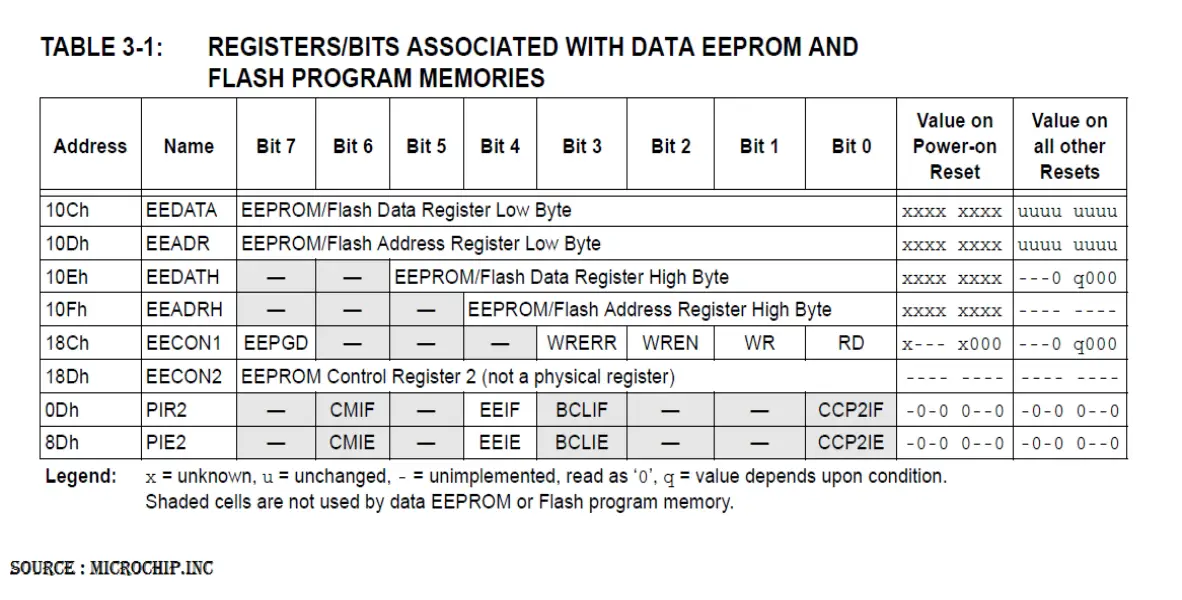

The data EEPROM and Flash program memory is readable and writable during normal operation by electrically erasing or direct writing methods. The memory of this register space is not directly mapped in the register memory space. It can be indirectly addressed through SFR registers. The commonly used SFR registers (for read and write this memory) for this purpose are given below.

• EECON1

• EECON2

• EEDATA

• EEDATH

• EEADR

• EEADRH

When interfacing a data memory location into this EEPROM, the EEDATA holds 8 bit data (for reading and writing) and the register EEADR holds the address of the EEPROM location. The PIC16F8XX devices have 128 or 256 bytes of data EEPROM (depends on the type of devices).

The address range of EEPROM memory starts from 00h to FFh (256 byte devices) and 80h to FFh (128 bytes devices). When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the program memory location being accessed. These devices have 4 or 8K words of program Flash, with an address range from 0000h to 0FFFh for the PIC16F873A/874A and 0000h to 1FFFh for the PIC16F876A/877A. Addresses above the range of the respective device will wrap around to the beginning of program memory. The EEPROM data memory allows single-byte read and writes.

The Flash program memory allows single-word reads and four-word block writes. Program memory write operations automatically perform an erase-before write on blocks of four words. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations. When the device is code-protected, the CPU may continue to read and write the data EEPROM memory.

EEADR and EEADRH

EEADR register pair can be address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LS (least significant) Byte of the address is written to the EEADR register. When selecting a program address value, the MS Byte (most significant) of the address is written to the EEADRH register and the LS Byte (least significant) is written to the EEADR register. If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

EECON1 and EECON2 Registers

EECON1 is memory accessible control register. The control bit, EEPGD, determines the type of memory that will be access (program memory or data memory). When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write or erase, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation. The WREN bit, when set, will allow a write or erase operation. On power-up,

The WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a MCLR or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers. Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software. EECON2 is not a physical register. Reading EECON2 will read all ‘0’s. The EECON2 register is used exclusively in the EEPROM write sequence. The structure of this register module is given below.

| R/W-X | U-0 | U-0 | U-0 | R/W-X | R/W-0 | R/S-0 | R/S-0 |

| EEPGD | ———— | ———— | ————- | WRERR | WREN | WR | RD |

- Bit 7 (EEPGD): Program/Data EEPROM Select bit which select program memory or data memory according to the applications. If this bit is ‘1’, it can be access program memory and if this bit is ‘0’ ,it can be access data memory.

(1 = Accesses program memory

0 = Accesses data memory)

- Bit 6-4 (Unimplemented): Read as ‘0’

- Bit 3 (WRERR): this bit used as an EEPROM Error Flag bit

(1 = A write operation is prematurely terminated (any MCLR or any WDT Reset during normal operation)

0 = the write operation completed)

- Bit 2 (WREN): this bit generally acts as an EEPROM Write Enable bit

(1 = Allows write cycles

0 = Inhibits write to the EEPROM)

- Bit 1 (WR): Write Control bit which control the writing instructions.

(1 = Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.

0 = Write cycle to the EEPROM is complete)

- Bit 0 (RD): Read Control bit which controls the read instructions.

(1 = Initiates an EEPROM read; RD is cleared in hardware. The RD bit can only be set (not cleared) in software.

0 = Does not initiate an EEPROM read)

Registers/bites that associated with data EEPROM and FLASH program memories in PIC16F877 are given in the table below.

4 Comments

very helpful thank you 🙂

can any one of you to tell me little information about this project now please EEPROM/FLASH Memory Organization in PIC 16F877

fussy logic ic fabrication and programming is very informative in todays electronics industry. I should post an article about this as per your request after completing my PIC articles

dear sir,

this article is very informative. similarly can you publish details of “fussy logic” Ics and programing details used in domestic washing machines

thank you